- Úvod do PLD a jazyka VHDL

- Základní konstrukce ve VHDL

- CPLD a první aplikace

PLD neboli Programovatelné Logické Obvody jsou digitální obvody, jejichž funkci lze libovolně měnit/programovat. Stejně jako se dá mikrokontrolér naprogramovat a tím změnit software, který se vykonává, lze PLD naprogramovat a tím změnit hardware. Velmi zjednodušeně si je můžete představit jako velké množství logických hradel (NANDů, NORů, …), ze kterých lze vhodným naprogramováním složit libovolný digitální (kombinační i sekvenční) obvod.

Ačkoliv mají PLD zajímavou a dlouhou historii a existuje jich více druhů, zaměřím se v dalším textu pouze na obvody CPLD a FPGA, které jsou v současné době nejzajímavější. Také se dopustím malého zjednodušení a budu obvody CPLD a FPGA souhrně nazývat PLD, ačkoliv to není zcela technicky přesné.

Snad jenom pro zajímavost – takovým jednoduchým programovatelným logickým obvodem může být i obyčejná paměť ROM. Adresní sběrnice slouží jako vstupy a datová jako výstupy. Jakmile na vstupy (adresu) přivedete požadovanou kombinaci, na výstupu se objeví předem nahraná kombinace. Můžete si tak vytvořit relativně velký kombinační obvod realizující velkou logickou funkci.

Obvody CPLD

Complex Programmable Logic Device jsou obvody s menším stupněm integrace a hodí se především pro aplikace s menší složitostí. Také se hodí především pro kombinační logiku. Sekvenční logika sice lze v CPLD realizovat, ale výsledek zabírá příliš mnoho stavebních bloků CPLD. Ty se nazývají makrobuňky (macrocells).

Při výběru CPLD je počet makrobuňek tím nejdůležitějším parametrem. Platí totiž přímá úměra – čím více makrobuňek, tím složitější a větší logické funkce můžeme realizovat. Dopředu je ale těžké odhadnout, kolik se do jedné makrobuňky vejde logických hradel. Jejich velikost i složení se totiž u každého výrobce liší. Vezněme za příklad firmu Xilinx a jejich CPLD XC9572XL. Tento obvod patří do rodiny XC9500XL (napájení 3,3V, vstupy jsou tolerantní).

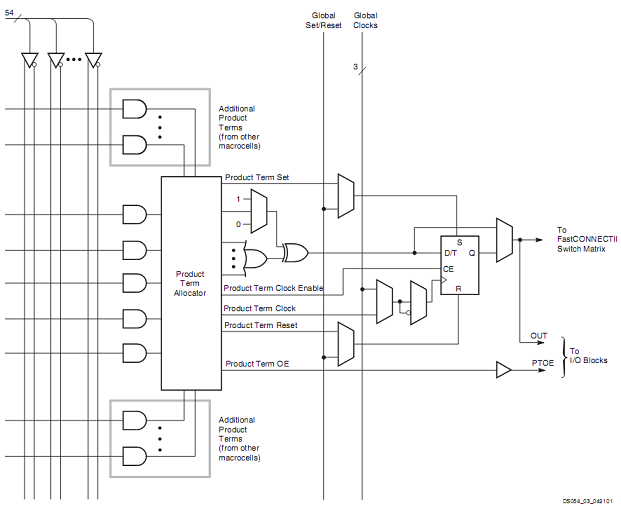

Na obrázku je znázorněno schéma jedné makrobuňky tohoto obvodu. Na levé straně je vstupní matice složená z ANDů. Tyto vstupy lze napojit na tzv. P-termy, kterých je v každé buňce pět. Pokud je ale potřeba více P-termů v jedné buňce, lze si další vypůjčit u sousedních makrobuňek. Tyto P-termy jsou pak pomocí Product Term Allocatoru pospojovány podle potřeby a výstup je přiveden buď na výstup makrobuňky (ten může být spojen s výstupním pinem obvodu, nebo se vstupem další makrobuňky), nebo na klopný obvod, který může být podle potřeby typu T nebo D. Každá makrobuňka má také globální signály Set/Reset a Clock.

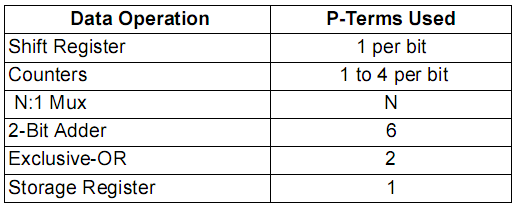

Pro představu ještě tabulka, která znázorňuje kolik P-termů je potřeba k realizaci různých sekvenčních obvodů.

Například jeden 5 bitový posuvný registr zabere 5 P-termů a tedy jednu makrobuňku. Na druhou stranu, 15 bitový registr zabere 15 P-termů, ale také jednu makrobuňku (nicméně 2 sousední se stanou nepoužitelnými a tutíž prakticky přijdeme o 3 makrobuňky).

Zmiňovaná rodina CPLD XC9500 se vyrábí s 36, 72, 144 a 288 makrobuňkami. Z výše uvedeného si lze udělat představu, k jakým aplikacím se CPLD obvody hodí. Např:

- rozhraní mezi 5V a 3,3 nebo 2,5V logikou,

- dekodéry BCD, 1-z-N, Grayova kódu, atd…,

- řadiče 7 segmentových displejů,

- rozhraní pro složité obvody (např. mezi MCU a paralelní pamětí),

- rozšíření počtu použitelných pinů u MCU,

- a další.

Svou jednoduchostí a cenou se obvody CPLD hodí i pro začátečníky. Navíc je naprogramovaná struktura non-volatilní, takže po odpojení napájení zůstává v obvodu uložena. Není tedy nutné jej pokaždé programovat.

Obvody FPGA

Field-Programmable Gate Array jsou svou vnitřní strukturou mnohem složitější a zásadně se liší od obvodů CPLD. Hodí se na realizaci sekvenčních logických obvodů (i tak složité jako celé mikroprocesory, nebo digitální filtry).

Základním stavebním prvkem FPGA jsou konfigurovatelné logické bloky (CLB). Ty obsahují několik slice a ty obsahují logické buňky (logic cell) z nich každá obsahuje look-up tabulku (LUT), klopný obvod typu D a někdy také úplnou sčítačku, případně další bloky.

Kromě CLB ale moderní FPGA obvody obsahují i několik bloků paměti RAM, obvod generující hodinové signály o různých frekvencích a různě fázově posunuté (nejmodernější FPGA mohou pracovat až na frekvencích 500 MHz a více), některé typy obsahují i bloky pro DSP, sčítačky, násobičky, atd…

Pro představu si vezmeme rodinu FPGA Spartan 3A od firmy Xilinx. Konkrétně typ XC3S200A. Tento obvod je jeden z jednodušších a levnějších (cca do 300 Kč). Obsahuje 200 tisíc hradel, což představuje 1584 logických buňek. Máme tedy k dispozici 1584 LUT a klopných obvodů D, které jsou strukturovány do sliců a do CLB. V takovémto obvodu lze realizovat jednoduchý procesor s velmi omezenou instrukční sadou a paměť pro program může být přímo v blokové RAM, kterou má tento obvod o velikosti 288 kb.

Naproti tomu high-endové FPGA (např. Virtex od firmy Xilinx) mohou obsahovat i miliony buňek a Mb paměti RAM. V takovém obvodu lze realizovat i složité procesory a ještě je spousta místa pro náročné aplikace (např. řízení A/D převodníku, CIC filtr spojený s procesorem a další často používané bloky v softwarovém rádiu).

Oproti CPLD obvodům mají FPGA volatilní paměť, takže po odpojení napájení se naprogramovaná struktura okamžitě vymaže. Je tedy nutné po každém zapnutí obvod nejdříve naprogramovat. Většinou se tento obvod programuje z externí FLASH paměti, která se k FPGA může připojit buď paralelně nebo sériově (SPI). Také lze během vývoje obvody programovat přes JTAG rozhraní.

Jazyk VHDL

K popisu hardwarové struktury PLD obvodů slouží v dnešní době vyšší programovací jazyky. Těch existuje několik, jmenujme například Verilog, ABEL nebo VHDL. Právě s VHDL pracuji a znám jej, a proto se v dalším textu zaměřím na něj.

Zatímco syntaxe Verilogu vychází z jazyka C, VHDL má své kořeny v jazyce Pascal. Pokud jste někdy s Pascalem přišli do styku, budou vám některé konstrukce ve VHDL povědomé.

VHDL původně vzniklo jako jazyk pro simulace hardwaru. Až později se začal používat k popisu reálných obvodů. Jeho výhodou je hardwarová nezávislost – můžeme psát kód ve VHDL a simulovat jej, aniž bychom předem věděli jaký hardware nakonec použijeme. Jeho nevýhodou je ale relativně velká “ukecanost” a časté opakování stejných bloků.

Příklad, na kterém si ukážeme jak vypadá syntaxe jazyka, implemetuje jednoduchý binární kodér:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.NUMERIC_STD.all;

entity ENCODER is

port (

A: in std_logic_vector (7 downto 0);

Y: out std_logic_vector (2 downto 0)

);

end entity ENCODER;

architecture ARCH of ENCODER is begin

process (A) begin

case A is

when "00000001" => Y <= "000";

when "00000010" => Y <= "001";

when "00000100" => Y <= "010";

when "00001000" => Y <= "011";

when "00010000" => Y <= "100";

when "00100000" => Y <= "101";

when "01000000" => Y <= "110";

when "10000000" => Y <= "111";

when others => Y <= "ZZZ";

end case;

end process;

end architecture ARCH;

V sekci library se importují potřebné knihovny, ve kterých jsou definovány datové typy, aritmetické operace a další. Sekce entity popisuje vstupy a výstupy bloku ENCODER, který se snažíme popsat. V našem případě má blok vstup A o šířce 8 bitů a výstup Y o šířce 3 bity a oba jsou typu std_logic_vector.

Následuje sekce architekture, ve které je vlastní kód bloku. V našem případě se jedná o switch s 8 možnými kombinacemi. Pokud se na vstupu objeví kombinace "00000010", na výstupu se okamžitě objeví "001". Jedná se tedy o encodér kódu 1-z-8 na binární kód.

Všimněte si hlavně řádku when others. Pokud by se na vstupu objevila jakákoliv nedefinovaná kombinace, výstup se přepne do stavu vysoké impedance (Z).

Jazyk není case-sensitive, takže nezáleží na velkých a malých písmenech. Z vlastní zkušenosti ale doporučuji, abyste si zvolili jeden kódovací styl a toho se drželi. Není dobré v jednom souboru míchat ENCODER, Encoder a encoder. Z pohledu překladače se jedná o stejné entity, ale programátora to jenom mate.

Jakmile jsme takto popsali chování našeho bloku, je nutné jej instantizovat, přiřadit vstupy a výstupy reálným pinům reálného obvodu a celý kód přeložit a naprogramovat do obvodu. O tom ale až někdy příště, protože se jedná o dosti rozsáhlé téma. Vývojová prostředí od výrobců PLD obvodů tento postup také neusnadňují, spíše naopak.

Závěr

V tomto článku jsme si velmi stručně představili dva významné typy PLD obvodů – CPLD a FPGA. Zatímco CPLD jsou relativně malé a levné a hodí se k realizaci kombinačních obvodů a velmi výjimečně pro sekvenční obvody, FPGA jsou mnohem větší, dražší a používají se hlavně k realizaci sekvenčních logických obvodů.

V dalším článku bych chtěl na praktickém příkladu ukázat programování obvodu CPLD firmy Xilinx – XC9572XL. Tento obvod obsahuje 72 makrobuňek, napájí se 3,3V a jeho vstupy jsou tolerantní na 5V logiku. Na tomto obvodu si prakticky předvedeme používání vývojového prostředí Xilinx ISE Webpack (dostupné zdarma na webu Xilinxu, doporučuji nainstalovat předem, je to práce na několik hodin), napíšeme jednoduchý příklad výhradně ve VHDL a nakonec si ukážeme, jak obvod naprogramovat (k tomu bude zapotřebí nějaký JTAG programátor, který umí pracovat se soubory SVF nebo XSVF).

V některých dalších článcích bych pak rád představil vývojovou desku s tímto obvodem, na které zrovna pracuji.